Fine Beautiful Tips About What Are The Disadvantages Of PLL

Solved 7. For A Simple PLL Below, Please Answer The

Understanding the Downside

1. Cost Considerations with PLL

Phase-Locked Loops (PLLs) are undeniably useful little circuits, especially when you need a stable frequency or to synchronize signals. But like that fancy coffee machine that requires special filters, PLLs come with a few potential drawbacks. Let's dive into some of the key things that can make you think twice before slapping a PLL into your next project.

One of the most prominent concerns? Cost. A high-performance PLL can be more expensive than other frequency generation or synchronization methods. This is especially true if you need really clean output signals or wide operating frequency ranges. The precision components required to achieve top-tier performance simply aren't cheap. So, if you're on a tight budget, you might need to explore alternative solutions. Think of it as choosing between that artisan coffee and a perfectly acceptable cup of instant both will give you a caffeine kick, but one requires a bigger investment.

The increased complexity can also drive costs up. Designing and implementing a PLL requires more expertise than some simpler circuits. This might mean hiring someone with specialized knowledge, which translates to increased project expenses. It's like needing to call a plumber to fix a leaky faucet versus handling it yourself with a wrench the plumber knows what they're doing (hopefully!), but they definitely won't work for free.

Furthermore, the indirect costs associated with testing and troubleshooting a complex PLL should be factored in, as identifying the root cause of unwanted behaviors in PLL can be complicated. The more features a PLL has, the more the total cost of the components and assembly. It may be more economically and resource efficient to use a cheaper and simpler method.

2. Noise and Jitter

Another common disadvantage revolves around noise and jitter. While PLLs are designed to produce stable signals, they can actually introduce noise if not carefully designed. This noise can come from various sources, including the internal components of the PLL itself. Think of it like this: you're trying to create a perfectly smooth cup of coffee, but the grinder keeps spitting out tiny bits of coffee grounds. That's noise!

Jitter, which is essentially short-term variations in the output frequency, is another potential issue. Excessive jitter can wreak havoc in sensitive applications like high-speed data communication. Imagine trying to send a crucial message, but the words keep getting garbled because someone keeps bumping into the messenger. That's jitter affecting your signal.

Minimizing noise and jitter requires careful component selection, meticulous circuit layout, and a deep understanding of PLL design principles. It's not always as simple as just plugging in a chip and hoping for the best. You need to actively work to keep these unwanted guests from crashing your signal party.

External disturbances can also affect the PLLs output, if the components are not fully isolated. Electromagnetic interference, mechanical vibrations or temperature fluctuations will be transferred and amplified at the output.

3. Lock Time and Settling Time

PLLs aren't instantaneous; they take time to "lock" onto the desired frequency and stabilize the output. This lock time or settling time can be a significant limitation in applications that require rapid frequency changes. Imagine you're a DJ, and you need to seamlessly transition between songs. If your PLL takes too long to lock onto the new frequency, you'll end up with an awkward pause and a disappointed audience.

The lock time depends on several factors, including the PLL's loop bandwidth and the magnitude of the frequency change. A wider loop bandwidth allows for faster locking, but it can also increase noise. Finding the right balance between lock time and noise performance is crucial. It's a bit like trying to cook something quickly without burning it you need to carefully adjust the heat and timing.

In some cases, the lock time may be long enough to cause problems in real-time systems. If your application needs to respond quickly to changes in the input signal, a slow-locking PLL might not be the best choice. You might need to consider alternative techniques, such as Direct Digital Synthesis (DDS), which can switch frequencies much faster.

The delay may also be impacted by the temperature of the circuits, or the stability of the power supplied to the PLL. It is important to have a stabilized operating condition for reliable use.

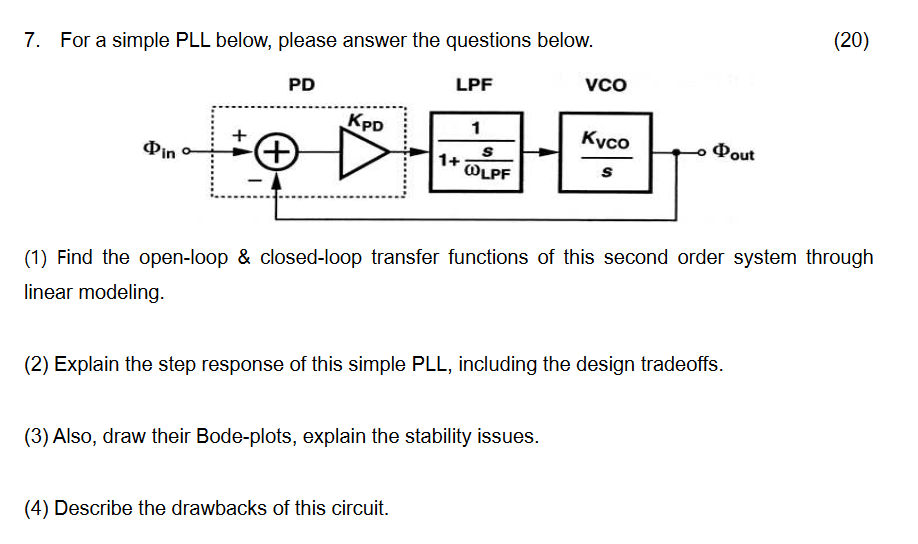

4. Loop Stability

Designing a stable PLL loop can be tricky. The loop dynamics need to be carefully analyzed to prevent oscillations or instability. Think of it as walking a tightrope you need to maintain your balance to avoid falling off. Similarly, a PLL needs to be properly tuned to stay stable.

An unstable PLL can exhibit all sorts of undesirable behaviors, such as spurious frequencies or erratic output. These problems can be difficult to diagnose and correct, especially if you're not familiar with PLL theory. It's like trying to fix a car engine without knowing anything about mechanics you might end up making things worse.

To ensure stability, designers often use simulation tools and perform extensive testing. The loop filter components, in particular, play a critical role in shaping the loop response and preventing instability. It's a balancing act, and a delicate adjustment of the filter is required.

An improper layout of the feedback loop may introduce electromagnetic disturbances which causes the system to oscillate. Having some experience or hiring an electrical engineer may be required to ensure stability of the device.

5. Design Complexity and Expertise

Let's be honest: PLLs can be complex beasts. Designing and implementing a robust PLL requires a solid understanding of feedback control theory, analog circuit design, and signal processing. It's not something you can usually just pick up overnight. It requires dedication.

The sheer number of parameters that need to be considered can be overwhelming. Loop bandwidth, phase margin, damping factor, and VCO gain are just a few of the things you need to worry about. It's like trying to navigate a maze with a thousand different paths you need a good map (or a very good sense of direction) to find your way out.

Even with simulation tools, achieving optimal performance can be a challenging task. You might need to experiment with different component values, tweak the circuit layout, and fine-tune the loop parameters to get everything just right. Its an iterative process that requires patience and perseverance.

Often, the complexity also increases as the specifications become tighter. For example, a PLL designed for very low jitter performance may require significantly more complex architecture and design efforts than a basic frequency synthesizer. So understanding the trade-offs and limitations is the key to achieve a good outcome.

Frequently Asked Questions

6. What are the main applications where the disadvantages of PLLs can be a significant concern?

In high-speed data communication, where jitter and noise can directly impact data integrity. Also, in applications requiring extremely fast frequency switching, such as frequency hopping spread spectrum systems, the lock time limitations of PLLs become critical.

7. How can I mitigate the effects of noise in a PLL design?

Careful component selection is important, particularly low-noise amplifiers and voltage-controlled oscillators (VCOs). Also, proper filtering techniques, such as using a well-designed loop filter, can help to reduce noise. Shielding the PLL from external electromagnetic interference can also be beneficial.

8. Are there alternative technologies to PLLs that overcome some of these disadvantages?

Yes, Direct Digital Synthesis (DDS) offers faster frequency switching and can generate a wider range of frequencies with more flexibility. However, DDS may have its own limitations regarding power consumption and spectral purity, depending on the specific implementation.

Digital PLL Frequency Synthesizers What They Are, How Work YouTube

PLL Algorithms For Rubik's Cube Learning To